Evolving pluggable optics to reduce power consumption

Optical networking is undergoing a significant transformation, fueled by surging bandwidth demand from artificial intelligence (AI). In fact, inside the data center, AI Ethernet networking is anticipated to require 335 exabits per second of bandwidth by 2030, almost 60 times higher than in 2024.1

AI workloads, combined with other traffic, are putting immense pressure on networks — not just for bandwidth, but also for power and space, resources that don’t scale linearly with data demand, given constraints in electrical supply, cooling and rack and aisle space. Data centers consumed ~1.5 percent of the world’s electricity in 2024 (415 terawatt-hours (TWh), which is set to more than double, to ~945 TWh by 2030. 2

While coherent pluggables are optimized for metro, regional and long-haul distances, intra-data center connectivity, typically under 500 meters, is moving to high-efficiency pluggables to meet strict power and thermal constraints.

Reducing power consumption in pluggables

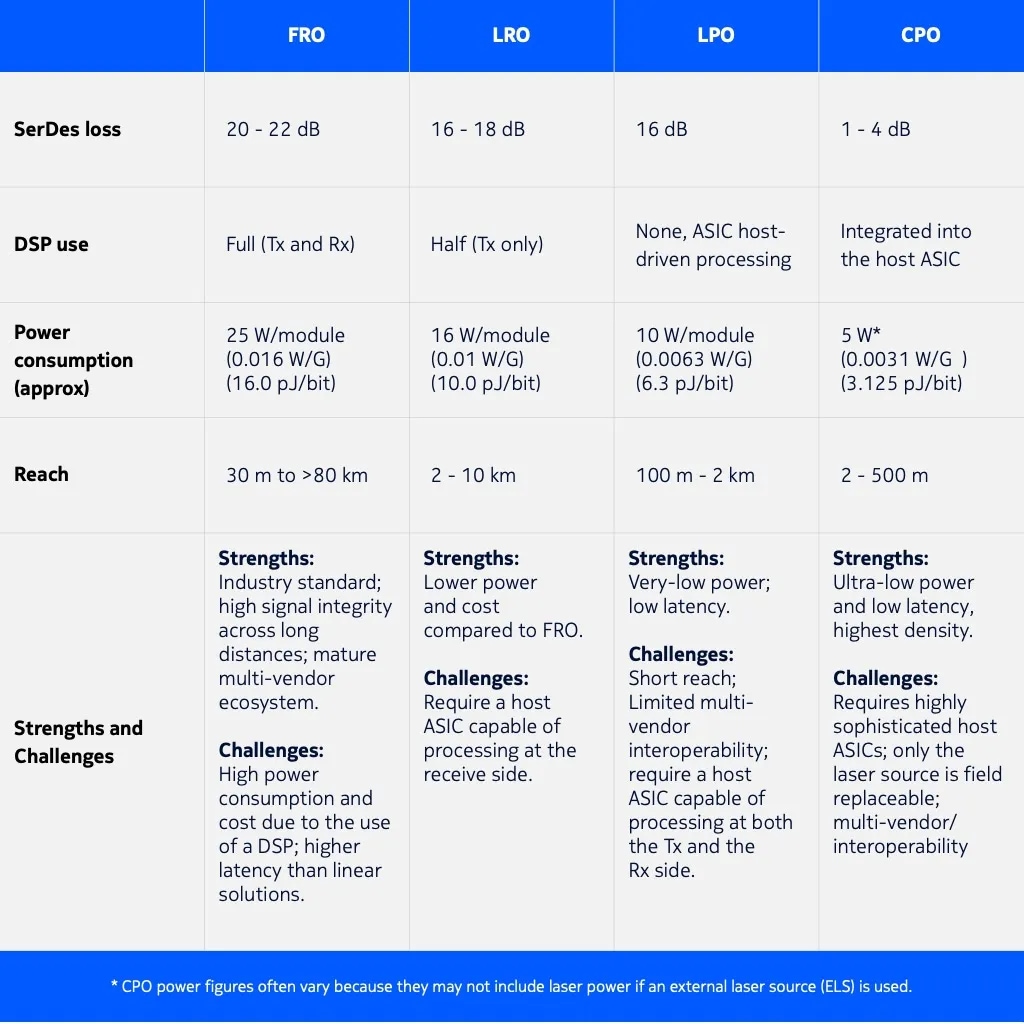

One factor affecting power consumption in high-speed optical pluggables is SerDes loss. It varies based on how far the electrical signal travels from the host ASIC to the optical interface. SerDes lane length is directly proportional to power consumption, as longer links require more energy and processing power from the digital signal processor (DSP) to maintain signal integrity over distance. Reducing the electrical SerDes lane count or length, therefore, reduces power consumption. Maximum optical transmission reach is determined by the trade-off between energy efficiency and the signal processing power available to correct distortions.

Designs for intra-data center connectivity are described below:

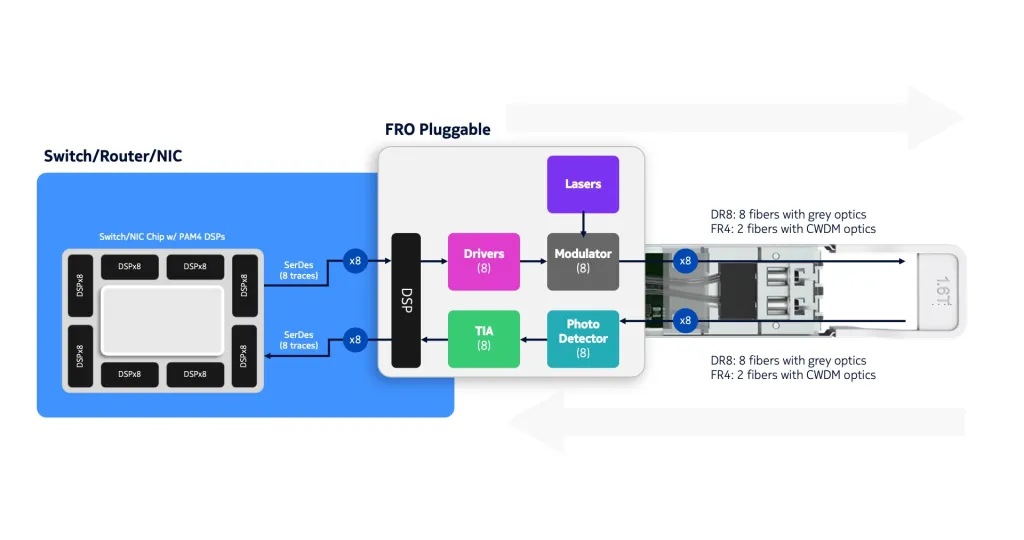

- Fully retimed optics (FRO): In FRO, both the transmit (Tx) and receive (Rx) paths use a PAM4 DSP to retime and recover signals. Electrical traces typically introduce up to 22 dB of loss between the host ASIC and the pluggable, requiring retiming to maintain signal integrity and reach. This improves performance but increases power consumption and latency. The DSP also performs forward error correction to enable reliable transmission over longer distances. FRO modules remain widely deployed, particularly for links over 10 km. Figure 1 shows the main building blocks of a typical FRO.

Figure 1: Building blocks for fully retimed optics.

FRO’s higher-power-per-bit makes it less well suited for short reach datacenter links (e.g., under 500 m). This has driven development of the three following approaches, which combine or eliminate functions and reduce energy consumption by as much as 70 percent while delivering capacity up to 1.6 Tb/:

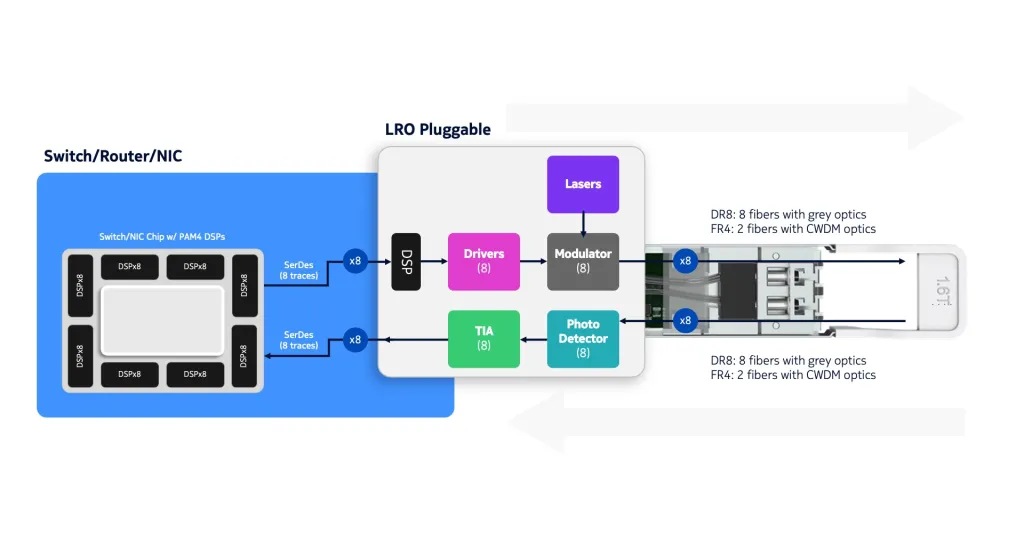

- Linear receive optics (LRO), or half retimed or Transmit re-timed optics (TRO): LRO reduce power consumption by limiting DSP retiming to Tx. Since the DSP draws the most power in a pluggable, removing Rx retiming lowers overall module power. In LRO, the Tx path still uses a DSP to launch clean signals, while the Rx path operates linearly, pushing clock recovery and equalization to the host ASIC. Figure 2 depicts the building blocks of LRO.

Figure 2: Building blocks for linear receive optics.

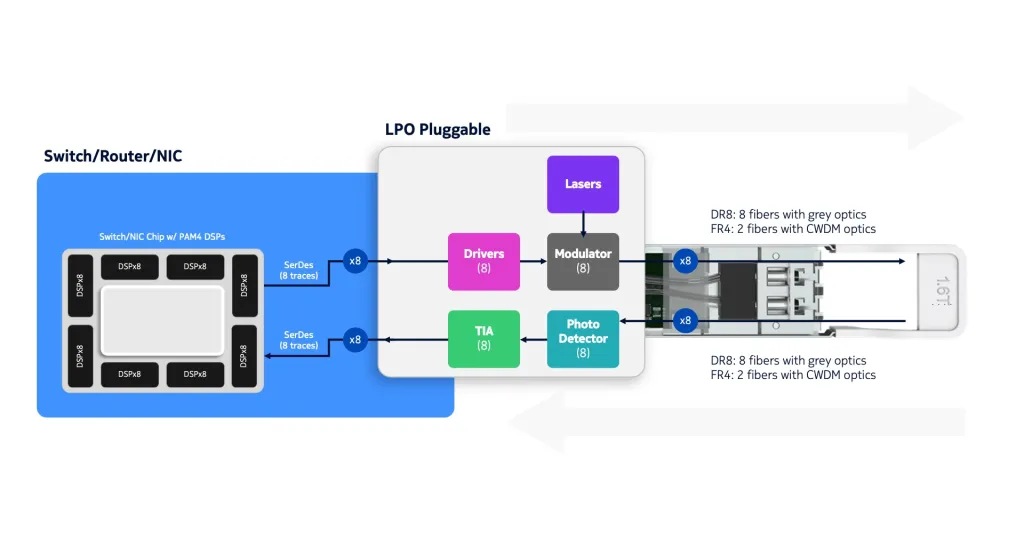

- Linear pluggable optics (LPO): In LPO, neither Tx nor Rx contain retiming circuitry. The optical module operates in a true linear mode, pushing unprocessed (raw) signals to the ASIC SerDes for equalization and clock recovery (Figure 3). Removing retiming dramatically reduces module power consumption. Without internal CDR/DFE logic, the host ASIC performs signal correction, making these optics lean, power-efficient and appealing for high-density and short-reach links (typically 100 - 500 m over multi-mode fiber, up to 2 km over single-mode). Note: no DSP means host ASICs with advanced equalization and linear analog front-end capabilities are required.

Figure 3: Building blocks for linear pluggable optics (LPO).

-

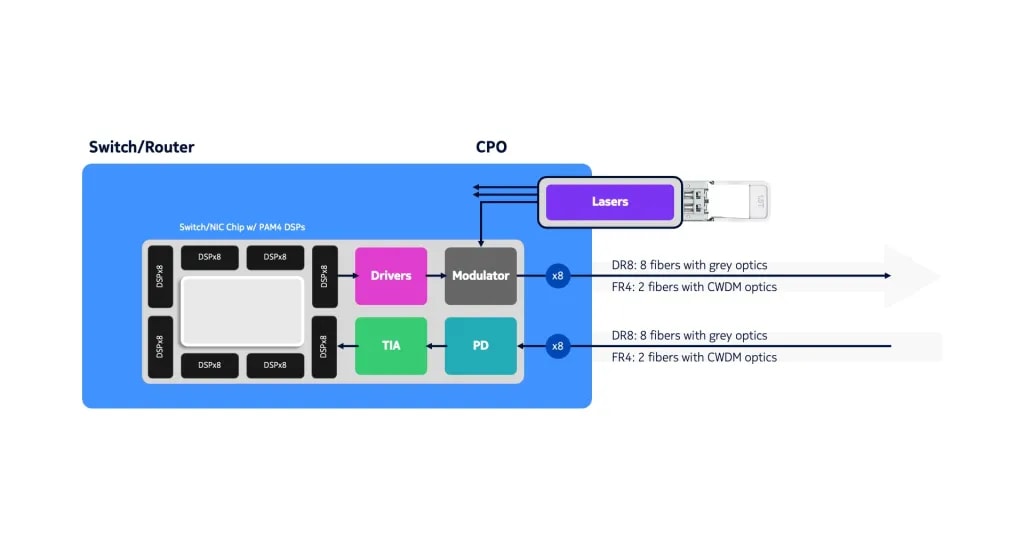

Co-packaged optics (CPO): Instead of sending electrical signals from host ASIC to optics over SerDes traces on the main circuit board, CPO integrates optics into the host ASIC, often on the same substrate. This shortens the electrical path and reduces SerDes losses to 1 - 4 dB. Optical conversion is moved to the switching/computing ASIC (Figure 4). By eliminating high-speed SerDes traces between host ASIC and optics, CPO drastically improves power per bit and latency compared to traditional pluggables. CPO is designed for ultra-short, high-density links. While it can technically reach 500 m, its sweet spot is scale-up networking (GPU to GPU), where it extends the range of copper-like performance from 2 m to 10 - 100 m.

Figure 4: Building blocks for co-packaged optics.

Table 1 summarizes the differences between these four designs.

Table 1: Comparison between all four architectural approaches.

Nokia’s intra-data center optical connectivity

With our U.S.-based optical semiconductor fab, Nokia's Infinite Capacity Engine – Data Center (ICE-D) intra-data center optical connectivity technology combines multiple optical functions onto a single monolithic chip for industry-leading density, low latency and power efficiency. Capable of supporting speeds over 3.2 Tb/s while reducing power per bit up to 75 percent, ICE-D technology can be implemented in FRO, LRO and LPO designs to help data center operators manage the exponential in intra-data center capacity growth driven by AI applications.

Optimizing power per bit: The path forward for intra‑data center optics

Power efficiency is a main factor driving pluggable optics evolution. As network speeds increase, it’s challenging to adapt traditional architectures, such as FRO, to meet stringent power and thermal limits, particularly in dense data center environments. LRO and LPO demonstrated meaningful power savings were possible by shifting signal processing to the host ASIC.

CPO shifts design thinking by moving optical conversion inside the host ASIC, however, it requires more sophisticated ASICs in host devices. This produces innovative architectures optimized for specific reach, cost and power requirements that will co-exist for the foreseeable time to maximize power efficiency and enhance networking flexibility.

References

[1] The 650 Group

[2] https://www.iea.org/reports/energy-and-ai/energy-demand-from-ai