Predicting the outage of microwave line-of-sight digital radio requires estimates of the dispersive characteristics of multipath fading.

© 2019 European Association of Geoscientists & Engineers Convolutional neural networks can provide a potential framework to characterize groundwater storage from seismic data.

This work studies the effects of sampling variability in Monte Carlo-based methods to estimate very high-dimensional systems.

A new methodology to statistically analyze the flux mobility of people in a city is described.

Efficient parametric fluorescence is obtained from a pump wavelength lambda=1.06 mu m in low-loss, form-birefringent GaAs/AlOx waveguides.

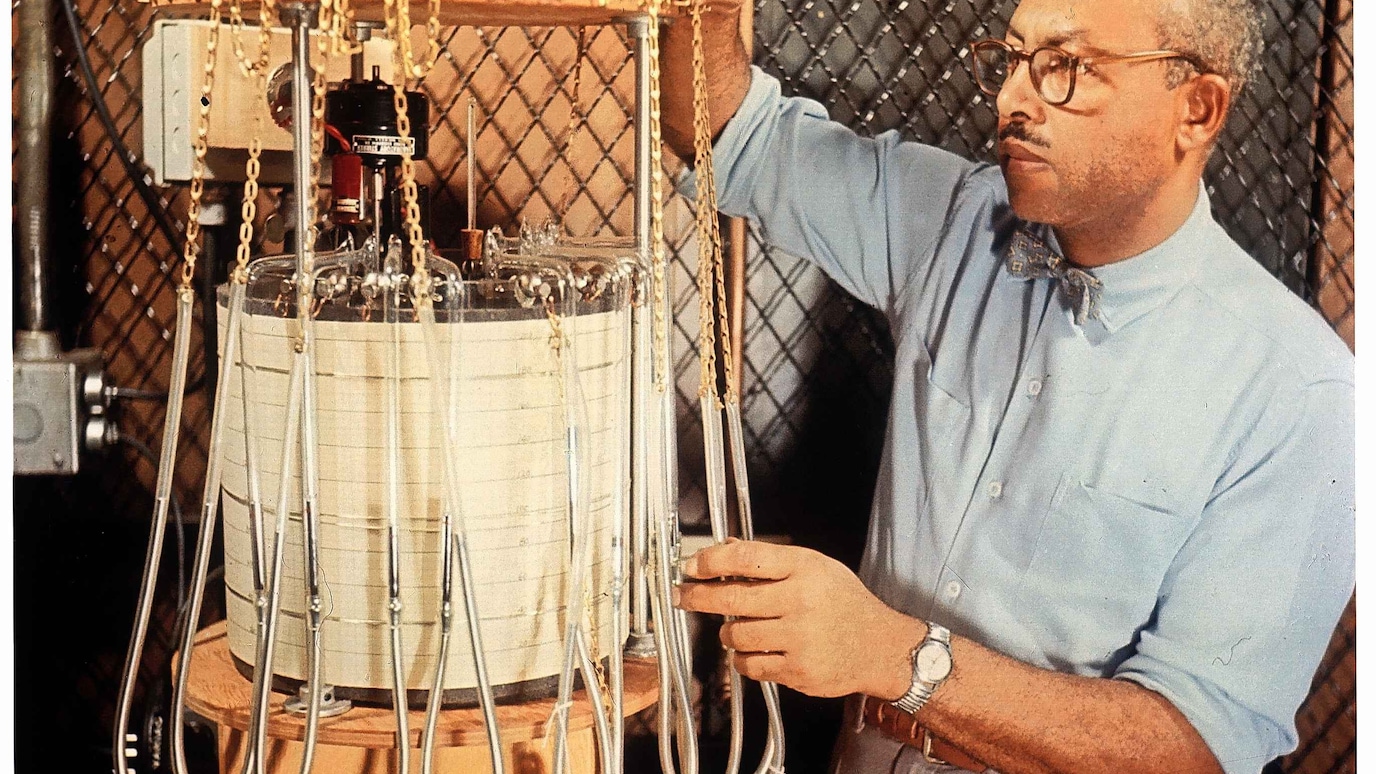

Trunk-group and point-to-point traffic data systems provide the measurements of telephone traffic which are used for the current and the long-range planning of the Bell System's Public Switched Net

Joint source-channel decoding of variable length codes for image and video streaming transmission over unreliable links, such as wireless networks, is a subject of increasing interest.

We investigate the feasibility of using hard-decision bit error rates or, alternatively, mutual information, both measured before a soft input forward error correction decoder, as a means to estima

An understanding of the relationship between chemical vapor deposition process parameters such as stoichiometry, temmperature and pressure and the properties of the resulting solid thin films is cr

We demonstrate that deep neural networks can be used to approximate the conditional distribution of a non-linear channel with memory.

Explore more

Video

AI-enhance wireless reliability: joint source and channel coding for robust 6G air interface

Blog

Blog

Podcast